降低BOOST辐射EMI

转载:

https://www.toutiao.com/article/7283432871191298595/?log_from=5b1526201783f_1697590210040

1.Boost型DC-DC辐射EMI分析

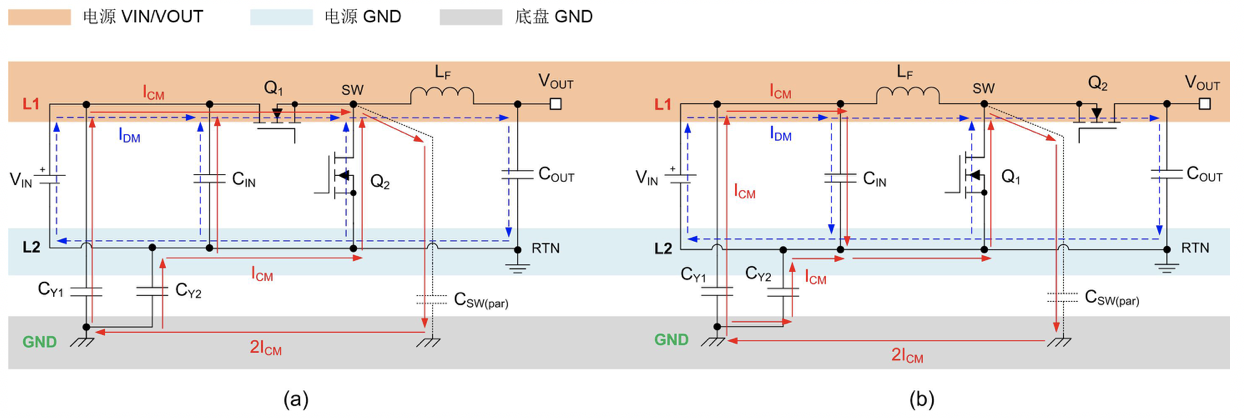

图10-1是典型的同步Boost电路,由输入电容Cin,电感L,开关器件Q1、Q2以及输出电容Cout组成,同时形成4个回路。

Loop2和Loop3为开关电流断续回路,具有高di/dt和dv/dt,因此SW节点振铃明显。Loop1和Loop4虽然是存在反复充电放电,但却是电流连续回路,电感电流连续,高频噪声主要来源于SW节点开关高频噪声的传导,由于Q2电流断续(Boost的特征),Cout的容值大小以及位置决定了Loop4中Vout节点高频噪声幅值。

图10-1:BOOST开关回路分析

图10-2为SW节点典型的开关波形(输出仅放置Bulk电容),SW开关节点振铃幅值高达10V,震荡频率为200MHz左右。

图10-2:SW开关节点波形

图10-3是对应于图10-2的实际辐射EMI测试结果,采用3m方法,蓝色为垂直方向,红色为水平方向。测试结果显示噪声在频域上的峰值在200MHz附近,与时域测试结果图10-2吻合,因此抑制辐射EMI峰值意味着需要大幅度降低SW节点的振铃幅值,以及振铃周期数。

图10-3:辐射EMI测量幅值(CE测试标准)

2.BOOST输出电容选择

如图10-1所示,Boost的Cout选择有几个关键考虑点:

1:输出纹波幅值

2:系统稳定性需求

3:SW节点的振铃幅值

4:输出电容耐压等级(陶瓷电容容值随耐压增加而衰减)。其中1、2、3、4与SW节点振铃幅值,辐射EMI息息相关。

图10-1中输出回路3(包含Q2、Cout)是断续回路,必须连接一个100nF-1uF去耦电容,该去耦电容对于降低SW振铃幅值有着关键作用。

为了获得低的输出纹波,建议选择低ESR陶瓷电容, 通常3~4颗22uF的X5R电容可以满足大多数应用,更大的容值有利于输出电压动态响应。鉴于陶瓷电容随着电压增加,容值减小的特性,建议选择电容耐压时考虑留有足够的余量。例如输出电压12V,建议至少选择20V或者25V耐压电容以维持足够有效的电容值。

根据输出纹波幅值要求,可以利用如下公式计算最小需求电容值Cout。

其中Vripple_C是输出纹波幅值,Vripple_ESR是输出电容ESR导致的纹波,I_Lpeak是电感电流峰值,ESR是输出电容的ESR。

3.Layout注意点

1:由于输出回路是开关回路,高di/dt和dv/dt,减小回路面积至关重要,输出回路去耦电容必须放置在离Vout、GND管脚最近的位置,从而降低SW振铃幅值,如图10-4红色箭头所示,利用NC管脚作为输出功率地,从而更近一步降低输出回路面积,Vout、NC管脚铺铜尽量宽。

图10-4:推荐Layout

2:由于SW的高频振铃同样会耦合至输入端,输入Bulk电容需要尽量放置离电感、GND近的位置以减小输入回路面积,输入端去耦电容同样需要离Vin端越近越好。

3:下层大面积铺地,降低地回路阻抗,采用8mil的过孔连接上下大地,降低热阻。

4:从系统稳定性考虑, AGND与PGND单端相连,通过散热焊盘底部相连,(散热焊盘同时也是功率地)。当Vout添加上去耦电容,并严格按照版图注意事项布板,测试波形如下图10-5所示,SW振铃幅值降低到6V,同时震荡明显周期变少。

图10-5:添加去耦电容和推荐Layout

4.SW开关节点噪声吸收电路选择

在SW开关节点添加对地的RC高频噪声吸收电路如图10-6所示,可以直接降低SW节点振铃幅值,该吸收电路通过降低dv/dt来降低SW节点振铃幅值,因此该电路会牺牲小于1%的Boost效率。

图10-6:采用SW节点振铃吸收电路

SW高频噪声在200MHz附近,因此选择Rs=2Ω,Cs=2nF,图10-6为SW节点加上该吸收电路,测试结果为图10-7所示,相比于图10-2所示,SW幅值大幅降低(蓝色=SW、绿色=Vin AC)。

图10-7:添加SW振铃吸收电路,测试波形

基于无系统级的EMI滤波器,图10-8为添加SW节点RC吸收电路后辐射EMI测试结果,相较于图10-3,EMI峰值下降了20dB。

图10-8:辐射EMI测试结果(RC缓冲电路)

5.磁珠的选择

在系统级应用中,如果需要进一步降低辐射EMI,贴片式磁珠是最简单的选择。关于磁珠的选择,有下列几个注意事项:

1:磁珠的频率需要覆盖高频噪声频段,根据图10-3,该磁珠需要在100MHz~300MHz频段表现为高阻抗值。

2:磁珠的饱和电流需要30%高于实际工作的峰值电流。

3:磁珠的等效阻抗越低越好,有利于减少磁珠带来的功耗。